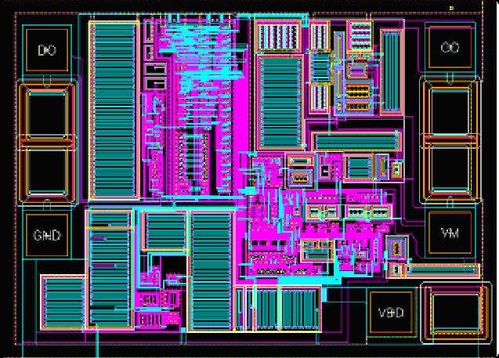

在集成電路(IC)設(shè)計(jì)的復(fù)雜流程中,軟件開(kāi)發(fā)是不可或缺的核心環(huán)節(jié),尤其在“總設(shè)計(jì)”這一高層次階段。它不僅僅是編寫代碼,更是連接硬件架構(gòu)定義與物理實(shí)現(xiàn)的關(guān)鍵橋梁。本文將深入探討集成電路總設(shè)計(jì)階段軟件開(kāi)發(fā)的主要任務(wù)、核心流程、關(guān)鍵技術(shù)以及未來(lái)趨勢(shì)。

一、軟件在IC總設(shè)計(jì)中的核心地位

在IC設(shè)計(jì)流程中,“總設(shè)計(jì)”通常指系統(tǒng)級(jí)設(shè)計(jì)、架構(gòu)定義和高級(jí)建模階段。此階段的軟件開(kāi)發(fā)主要服務(wù)于兩大目標(biāo):

- 系統(tǒng)建模與驗(yàn)證:通過(guò)軟件模型(如SystemC、UVM環(huán)境)對(duì)芯片的架構(gòu)、性能、功耗進(jìn)行早期仿真和評(píng)估,確保設(shè)計(jì)可行性。

- 設(shè)計(jì)自動(dòng)化與流程管理:開(kāi)發(fā)或集成各類電子設(shè)計(jì)自動(dòng)化(EDA)工具腳本、流程控制軟件以及數(shù)據(jù)管理平臺(tái),提升設(shè)計(jì)效率與質(zhì)量。

二、主要軟件開(kāi)發(fā)任務(wù)與流程

- 架構(gòu)探索與建模:

- 任務(wù):使用高級(jí)建模語(yǔ)言(如SystemC/TLM)創(chuàng)建芯片的系統(tǒng)級(jí)虛擬原型。

- 開(kāi)發(fā)內(nèi)容:編寫可執(zhí)行規(guī)約模型,模擬硬件模塊間的交互、數(shù)據(jù)流和整體性能,以便在硬件實(shí)現(xiàn)前進(jìn)行軟硬件劃分和架構(gòu)優(yōu)化。

- 驗(yàn)證平臺(tái)開(kāi)發(fā):

- 任務(wù):構(gòu)建強(qiáng)大的驗(yàn)證環(huán)境,以發(fā)現(xiàn)設(shè)計(jì)缺陷。

- 開(kāi)發(fā)內(nèi)容:基于UVM(通用驗(yàn)證方法學(xué))等標(biāo)準(zhǔn),開(kāi)發(fā)測(cè)試平臺(tái)、編寫激勵(lì)生成器、檢查器和覆蓋率收集代碼。這是確保芯片功能正確的關(guān)鍵軟件工作。

- 設(shè)計(jì)實(shí)現(xiàn)工具鏈與腳本開(kāi)發(fā):

- 任務(wù):自動(dòng)化完成從邏輯綜合、布局布線到時(shí)序簽核的物理設(shè)計(jì)流程。

- 開(kāi)發(fā)內(nèi)容:編寫Tcl、Python或Perl腳本,驅(qū)動(dòng)EDA工具(如Synopsys、Cadence系列工具),實(shí)現(xiàn)流程定制、任務(wù)自動(dòng)化及結(jié)果分析。開(kāi)發(fā)內(nèi)部工具以填補(bǔ)商用工具鏈的空白。

- 功耗、時(shí)序及可靠性分析軟件集成與開(kāi)發(fā):

- 任務(wù):集成分析工具并開(kāi)發(fā)定制分析模塊。

- 開(kāi)發(fā)內(nèi)容:編寫腳本處理工具輸出數(shù)據(jù),進(jìn)行統(tǒng)計(jì)分析;或開(kāi)發(fā)專用算法,對(duì)功耗、時(shí)序瓶頸和潛在可靠性問(wèn)題進(jìn)行深度挖掘和預(yù)測(cè)。

- 數(shù)據(jù)管理與協(xié)作平臺(tái)開(kāi)發(fā):

- 任務(wù):管理海量的設(shè)計(jì)文件、版本和工程數(shù)據(jù)。

- 開(kāi)發(fā)內(nèi)容:開(kāi)發(fā)或定制基于數(shù)據(jù)庫(kù)的版本控制系統(tǒng)、設(shè)計(jì)數(shù)據(jù)管理系統(tǒng),以及支持團(tuán)隊(duì)協(xié)作的儀表板和報(bào)表生成工具。

三、關(guān)鍵技術(shù)棧與挑戰(zhàn)

- 編程語(yǔ)言:

- 系統(tǒng)級(jí)/驗(yàn)證:SystemC/C++、SystemVerilog(用于驗(yàn)證)。

- 腳本與自動(dòng)化:Python(已成為主流)、Tcl、Perl。

- 高性能計(jì)算與工具開(kāi)發(fā):C/C++。

- 方法學(xué)與框架:UVM、OVM、ESL(電子系統(tǒng)級(jí))設(shè)計(jì)方法學(xué)。

- 核心挑戰(zhàn):

- 處理超大規(guī)模設(shè)計(jì)復(fù)雜度:需要高度模塊化、可重用的軟件架構(gòu)。

- 性能與精度平衡:建模和仿真需要在速度和準(zhǔn)確性間取得平衡。

- 多物理域協(xié)同:軟件需能處理電、熱、機(jī)械等多物理場(chǎng)耦合分析的需求。

- 與先進(jìn)工藝節(jié)點(diǎn)的適配:3D-IC、FinFET等新技術(shù)對(duì)設(shè)計(jì)軟件提出新要求。

四、未來(lái)趨勢(shì)

- 人工智能/機(jī)器學(xué)習(xí)的深度集成:利用AI/ML進(jìn)行設(shè)計(jì)空間探索、自動(dòng)布局布線、缺陷預(yù)測(cè)和驗(yàn)證優(yōu)化,是提升生產(chǎn)力的革命性方向。

- 云原生與高性能計(jì)算:設(shè)計(jì)平臺(tái)向云端遷移,利用彈性計(jì)算資源進(jìn)行大規(guī)模仿真和數(shù)據(jù)分析,軟件開(kāi)發(fā)需適應(yīng)云架構(gòu)。

- 開(kāi)放標(biāo)準(zhǔn)與開(kāi)源生態(tài):RISC-V等開(kāi)放指令集架構(gòu)的興起,帶動(dòng)了開(kāi)源EDA工具(如OpenROAD)和IP的發(fā)展,軟件開(kāi)發(fā)需擁抱開(kāi)源協(xié)作模式。

- 軟硬件協(xié)同設(shè)計(jì):隨著芯片-系統(tǒng)協(xié)同優(yōu)化需求加劇,軟件開(kāi)發(fā)將更早介入,與硬件設(shè)計(jì)深度互動(dòng),實(shí)現(xiàn)全棧優(yōu)化。

###

集成電路總設(shè)計(jì)階段的軟件開(kāi)發(fā),是智力密集型的系統(tǒng)工程,它融合了計(jì)算機(jī)科學(xué)、電子工程和算法設(shè)計(jì)的精髓。隨著芯片復(fù)雜度呈指數(shù)級(jí)增長(zhǎng),強(qiáng)大、靈活且智能的軟件工具鏈已成為決定設(shè)計(jì)成敗的關(guān)鍵因素。未來(lái)的IC設(shè)計(jì)工程師,必須是精通硬件原理的軟件專家,通過(guò)代碼賦能,駕馭日益復(fù)雜的硅世界。